三星电子公司计划明年推出先进的三维(3D)芯片封装技术,与晶台积电竞争。

这家总部位于韩国水原的芯片制造商将使用SAINT或三星高级互连技术技术,以更小的尺寸集成高性能芯片(包括AI芯片)所需的内存和处理器。

在SAINT品牌下,三星计划推出三种类型的技术——SAINT S,垂直堆叠SRAM存储芯片和CPU;SAINT D,涉及CPU、GPU等处理器和DRAM内存的垂直封装;以及堆叠应用处理器(AP)的SAINT L,知情人士周日表示。

在大多数情况下,当前的 2.5D 封装技术是水平并排组装不同类型的芯片。

消息人士称,三星的一些新技术,包括SAINT S,已经通过了验证测试,然而,三星将在与客户进行进一步测试后,明年推出商业服务。

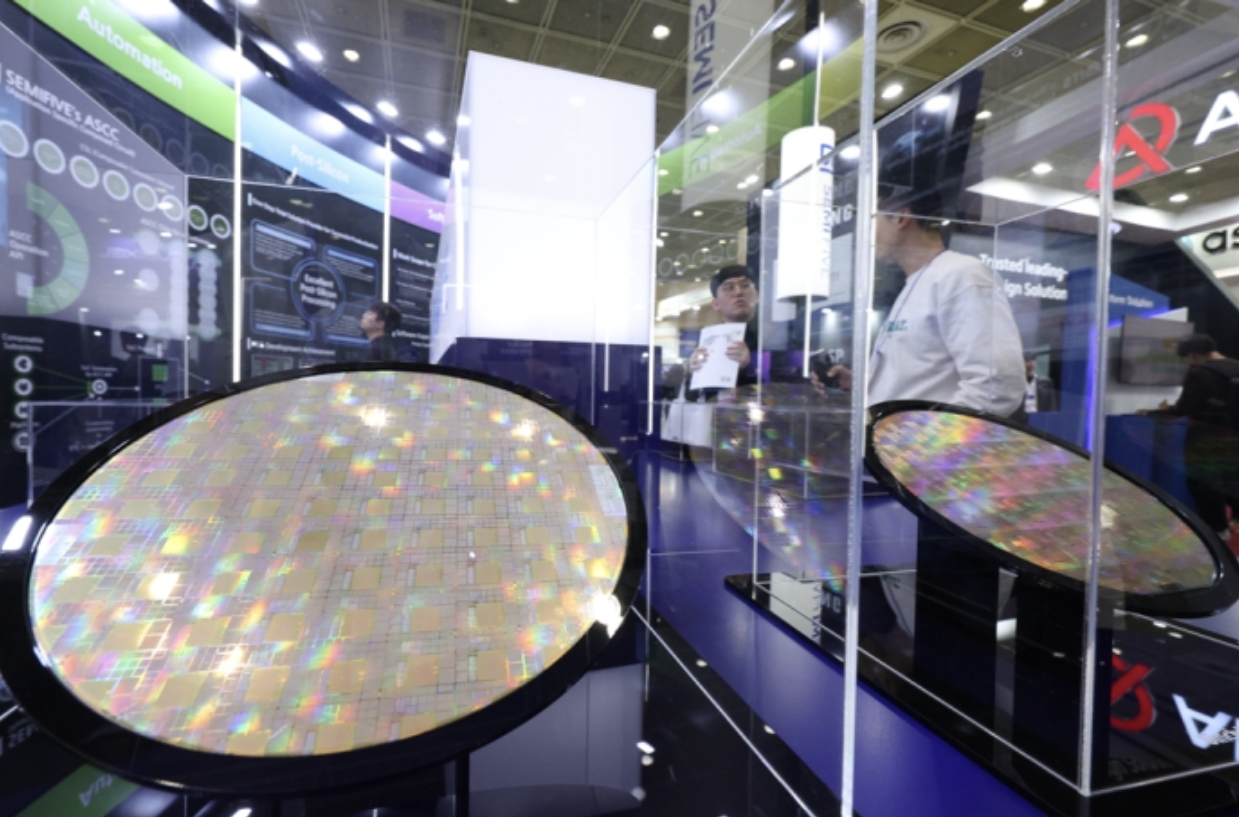

封装是半导体制造的最后一步,它将芯片置于保护壳中以防止腐蚀,并提供一个接口来组合和连接已经制造的芯片。

台积电、三星和英特尔等领先的芯片制造商正在激烈竞争先进封装,即集成不同的半导体或垂直互连多个芯片。先进的封装允许将多个设备合并并封装为单个电子设备。

封装技术可以帮助提高半导体性能,而不必通过超精细加工来缩小纳米,这在技术上具有挑战性,需要更多的时间。

根据咨询公司Yole Intelligence的数据,全球先进芯片封装市场预计将从2022年的443亿美元增长到2027年的660亿美元。在660亿美元中,3D包装预计将占约四分之一,即150亿美元。

目前业界的主流是2.5D封装,将芯片尽可能靠近,以减少数据瓶颈。

全球排名第一的合同芯片制造商台积电也凭借其十年前的2.5D封装技术成为全球先进封装市场的领导者。

台积电正在斥巨资为其客户(包括苹果公司和英伟达公司)测试和升级其3D芯片间堆叠技术SoIC。 台积电在7月份表示,将投资29亿美元建造一座新的国内先进封装工厂。