英特尔在 2021 年 7 月除了公布全新的电晶体架构 RibbonFET 以外,也宣布独创的背面供电技术 PowerVIA ,通过将供电架构自晶圆正面布线转移到背面进行直接供电,将晶圆上部全部用于讯号传输,结果即是使晶体管开关速度增加,同时能够在更小的面积占用实现与多鳍片设计同等的驱动电流; 在IEEE举办的VLSI 2023研讨会前夕,英特尔将展示PowerVIA的实践。

▲左边违现行供电位于晶体管上方、使供电与讯号需交错的设计,左方的 PowerVIA 将供电转移到下方直接供电、使晶圆上方仅存讯号线路

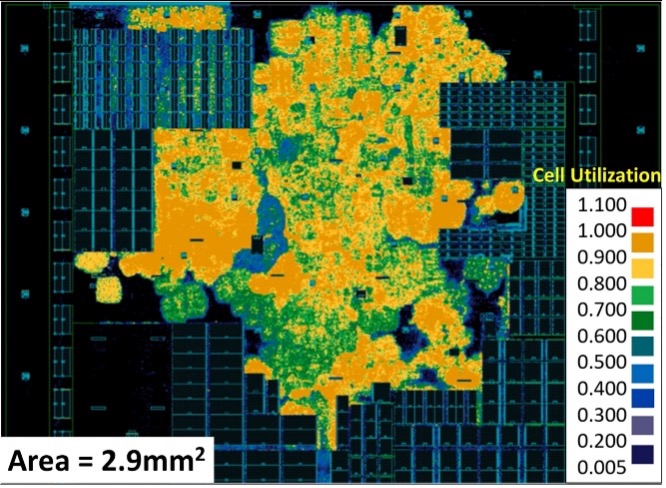

在VLSI研讨会官方推特的预告中提到,这是一颗采用PowerVIA全E Core的Intel 4制程芯片,从针脚设计酷似已经淘汰的LGA 1200针脚,最大的不同是原本现行英特尔芯片中央背面布满SMD电容的位置被PowerVIA技术的晶粒取代; 根据目前公布的数据,在2.9mm2的面积,能使能源使用效率达到90%并减少IR降压,最终的结果是使时钟提高5%。

▲ PowerVIA 相较传统晶圆上部供电能提升能源效率并缩短 5%时间

不过此次主要是针对PowerVIA的进行实践展示,根据英特尔的规划,PowerVIA并不会使用在Intel 4制程,至少要等到导入RibbonFET架构的英特尔 20A与英特尔 18A制程后才会用于消费级芯片,据称PowerVIA技术最快将在2024年出现在消费终端市场。